# Design of Transconductance Based CMOS Circuits: An Overview

### Eric A. M. Klumperink, Clemens H. J. Mensink

"Most circuits are MOST circuits"

#### Prof. A.J.M. van Tuijl<sup>\*</sup>, Prof. H. Wallinga

At or also at PHILIPS Semiconductor

University of Twente Department of Electrical Engineering Enschede, The Netherlands

MESA Research Institute

# Contents

- Introduction on Transistor Level Circuit Design

- A Design Philosophy for Linear CMOS Circuits

=> "Transconductance Based CMOS Circuits"

- Generation of linear two-port circuits with 2 VCCSs

- **Classification** of 2VCCS Circuits

- Applications examples

- Conclusions

# Introduction

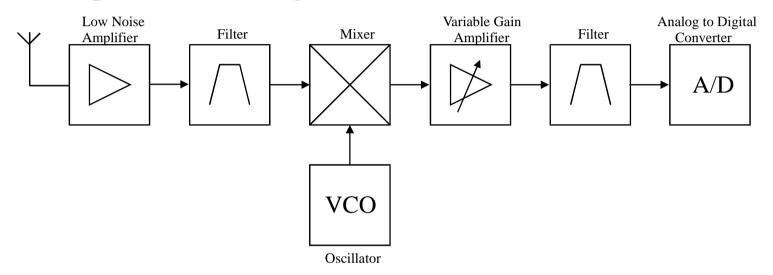

• Example of the analog section of a receiver IC:

- Use building blocks

- Linear blocks important: visible: amplifiers, filters

- "Invisible" (subblocks): V-I, I-V, buffers.

- At lowest level: Transistor level

# How to design transistor level building blocks?

• Literature: fragmentary, many circuit topologies!

- Questions: Variations on a few themes? Relative merits?

- CAD: analysis and optimisation of GIVEN topology

# Transistor level topology design??

• Huge number of possibilities!! => use heuristics, intuitions

Difficult to teach to students!

Teach intuition to a computer??

### **AIM: systematic methods:**

- Less chance of overlooking possibilities => better designs

- Basis for education and CAD

# A Design Philosophy for Linear MOS Circuits

Look at how most MOST Circuits are constructed:

- Combine simple basic circuits (differential pair, mirror) few components <=> HF, low noise, low current

- Use mainly saturated MOSTs (current output)

- Transconductance g<sub>m</sub> of MOST is crucial:

- Good model up to high frequencies

- Matching of transconductance is good (< 1%)

- Electronic variability

=> Self-correction

=> Adaptive signal processing

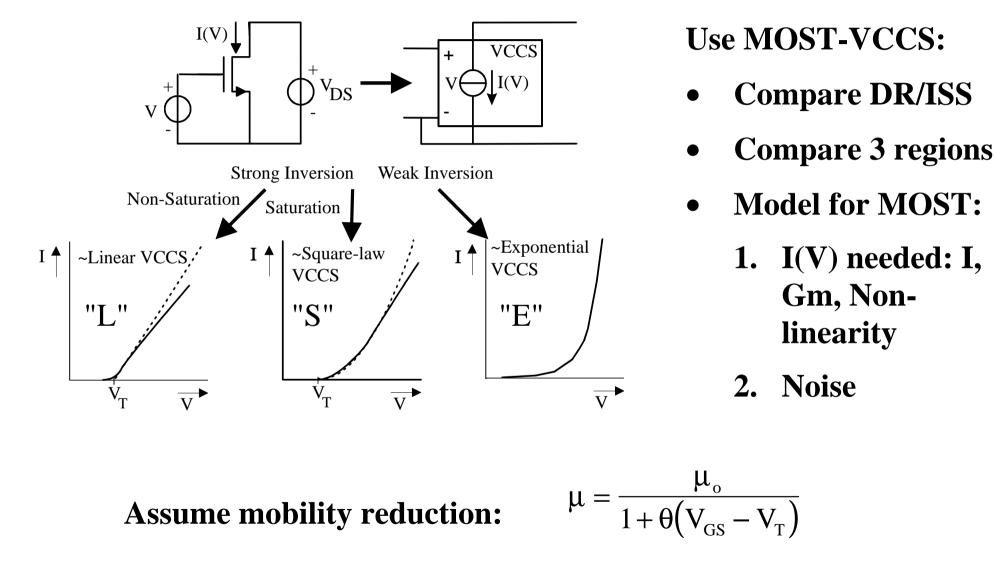

### PhD Thesis: Transconductance Based CMOS Circuits

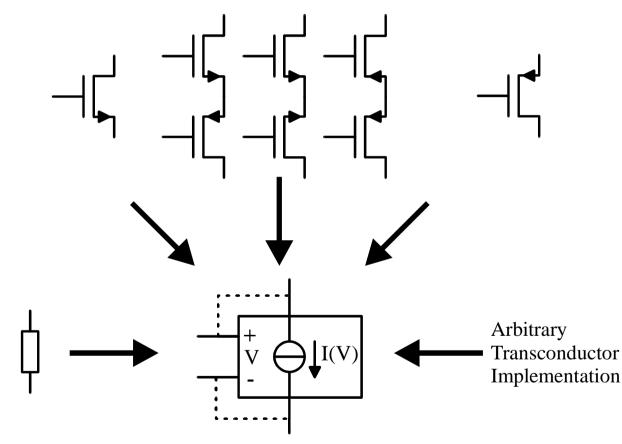

**Model components as Voltage Controlled Current Sources**

**Aim: Design linear circuit building blocks using VCCSs**

### Four main Questions:

What is needed for linear circuits? => REQUIREMENTS What is possible with using VCCSs? => CIRCUIT GENERATION Which are essentially different? => CLASSIFICATION What are their properties? => ANALYSIS OF CLASSES

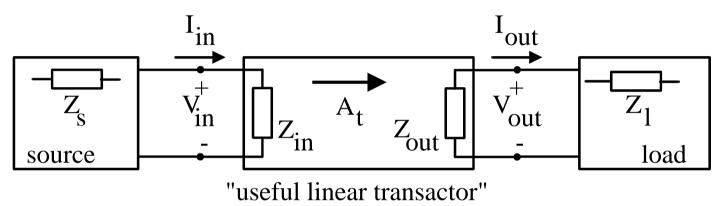

# **Requirements for linear circuit building blocks**

Model building block as linear two-port

Adapt to source/load [Nordholt, Huijsing]

$=> Z_{in} \text{ and } Z_{out}$ :  $\infty \lor 0 \lor Z_{exact}$ :  $=> 3 \ge 3$  "Transactors"

#### **Transfer function known or electronically controllable**

=> Two-port parameters: accurate or controllable

#### V-V and I-I, apart from V-I and I-V Transfers => 2 VCCSs

# **Generation of 2VCCS Circuits**

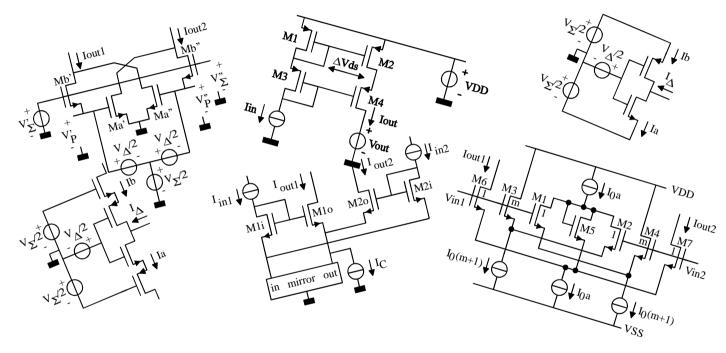

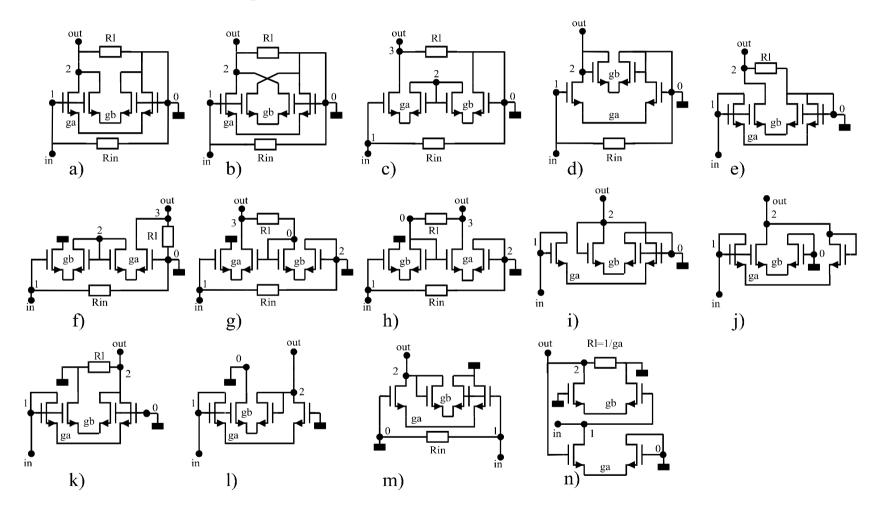

- All two-ports with 2 VCCSs generated using linear graphs

- Symbolic Analysis program to select useful ones:

=> 145 topologies with non-zero transfer function

- Each VCCS topology has several implementations

- All 3x3 transactors possible, directly or approximated

### **Application example:**

- Input Impedance matching Amplifier

- Implement all VCCS by differential pairs (simplicity)

### Example: Voltage Amplifiers with Zin=Rin

Hard to find by in non-systematic way!

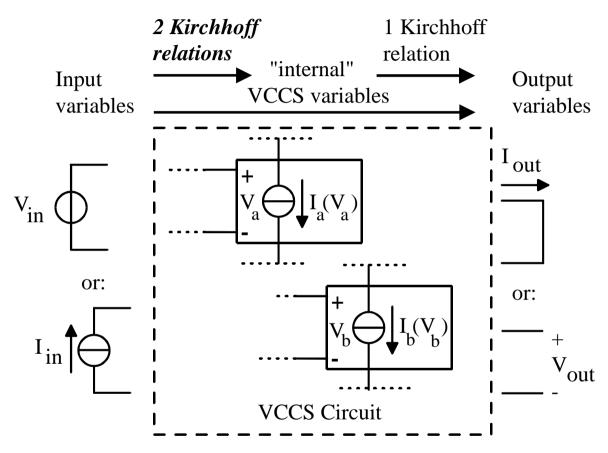

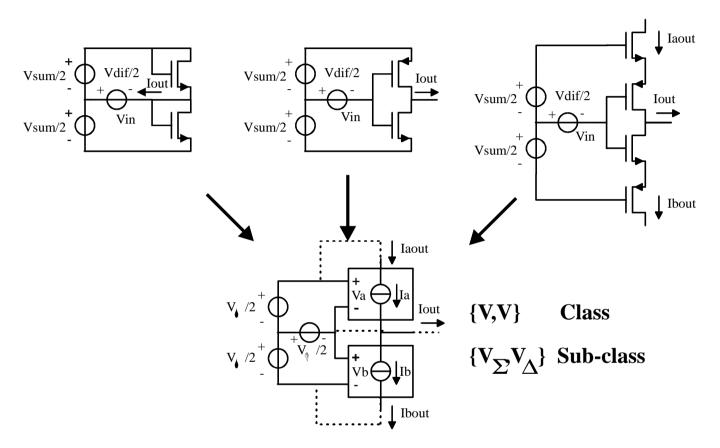

# **Classification of 2VCCS Circuits**

#### **Analyse electrical behaviour:**

- Two-port parameters

- Different possible solutions for the VCCS variables?

- 4 eqns needed (linear VCCS)

- $I_a = g_a V_a$  and  $I_b = g_b V_b$  available

- <u>2 additional</u> topology related <u>KVL/KCL</u> relations needed!

Non-linear case: square-law and exponential I(V): also 2 eqns.

#### Classification criterium: set of 2 independent Kirchhoff relations!

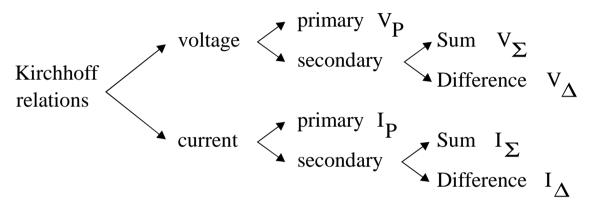

# All classes of 2VCCS Circuits

• Types of Kirchhoff relations:

• ALL Sets of 2 relations: 3 main classes and 14 subclasses:

|                         |                              |       | $\{V_P, I_{\Sigma}\}$        |

|-------------------------|------------------------------|-------|------------------------------|

|                         | $\{V_P, V_{\Sigma}\}$        |       | $\{V_{P},I_{\Delta}\}$       |

| { <i>V</i> , <i>V</i> } | $\{V_P, V_{\Delta}\}$        |       | $\{V_{\Sigma}, I_P\}$        |

|                         | $\{V_{\Sigma}, V_{\Delta}\}$ | {V,I} | $\{V_{\Delta}, I_P\}$        |

|                         |                              |       | $\{V_{\Sigma}, I_{\Sigma}\}$ |

|                         | $\{I_P, I_{\Sigma}\}$        |       | $\{V_{\Sigma}, I_{\Delta}\}$ |

| <i>{I,I}</i>            | $\{I_P, I_{\Delta}\}$        |       | $\{V_{\Delta}, I_{\Sigma}\}$ |

|                         | $\{I_{\Sigma}, I_{\Delta}\}$ |       | $\{V_{\Delta},I_{\Delta}\}$  |

### **Application Examples of the Classification**

- Recognise circuits as variations on a theme:

- 50 Published V-I Kernels in 4 classes!

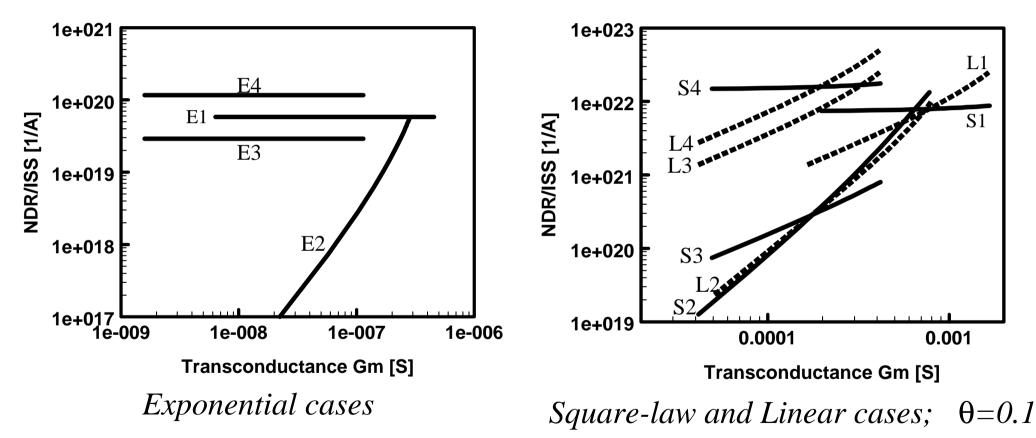

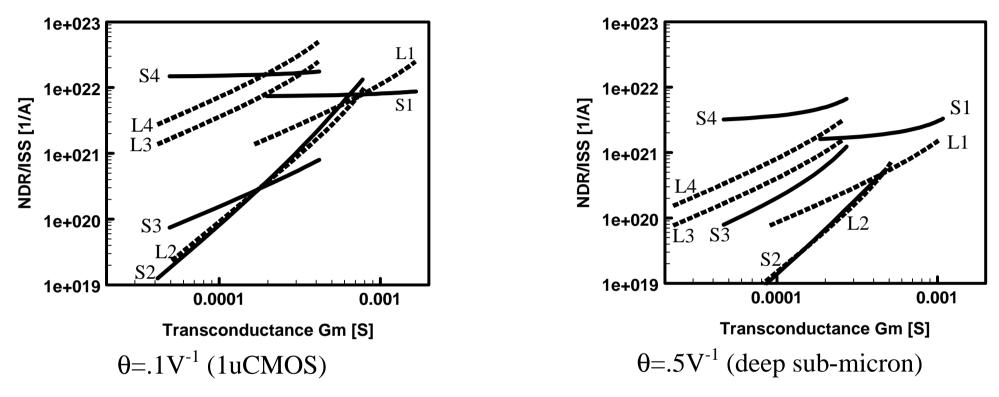

# Analyse DR/ISS of the 4 Classes of V-I Kernels

# **Compare 4 Classes of Circuits in 3 regions**

• NDR/ISS: Normalised to 100% HD3 (IP3), 1Hz NBW

• Weak inversion case much worse than strong inversion

### **Design Clues: compare 1\muCMOS with deep submicron**

- => worsened NDR/ISS, except differential pair (S3)

- MOST + Source resistance: maintains good NDR/ISS

- However: hardly any electronic variability

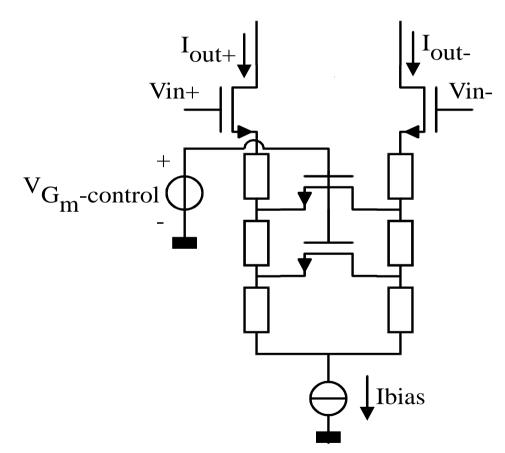

### Transconductor with "Soft-Switched" Resistors

**PhD Mensink: Resistors + MOST Switches**

- Body effect: different switching-level

- "gradually switched"

- Careful dimensioning

# Conclusions

#### Systematic approach to transistor level circuit design:

#### **Systematic Generation of circuits**

• Hundreds of circuits based on only 2 VCCS

### **Classification of ALL 2VCCS Circuits**

- Compact overview: 3 main classes and 14 subclasses

- Recognise variations on a theme

### **Analysis of classes of circuits**

• General design clues, e.g. use strong inversion if "square-law conformance", rely on resistors if not.

### Many transistor level circuit topologies are yet to be explored!