# **Reduction of 1/f Noise in MOSFETs by Switched Bias Techniques**

Eric A.M. Klumperink Sander L.J. Gierkink Arnoud v. d. Wel Gian Hoogzaad Hans Wallinga Bram Nauta UNIVERSITEIT TWENTE MESA Research Institute University of Twente PO Box 217 7500 AE Enschede The Netherlands

### Background

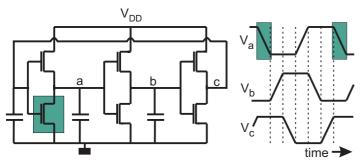

- Timing Jitter Analysis CMOS Ring Oscillator

- Cyclic jitter contribution of individual MOSTs

• Strong impact 1/f noise expected (correlation!)

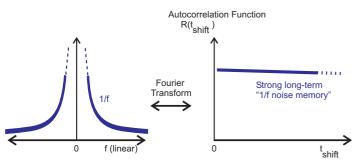

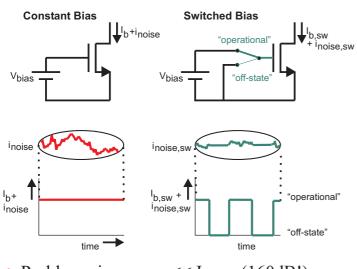

# 1/f Noise Reduction Hypothesis

- Measurements: low 1/f Noise contribution!!

- Question: could switching affect 1/f noise??

- => Do Switched Bias Experiment

• Problem:  $i_{noise,sw} \ll I_{b,sw} (160 dB!)$

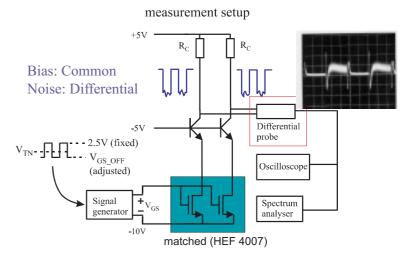

#### Switched Bias Measurement Setup

- Use matched devices and differential probe

- 60-80dB Common Mode Rejection Ratio!

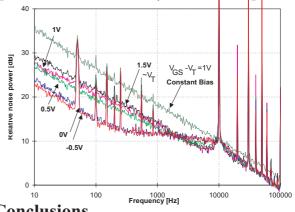

#### **Measurement Results**

- -6dB expected due to dutycycle 50%

- ✤ 6-8dB anamolous noise reduction!!!

- Observed in weaker form before at 100Hz [Bloom & Nemerovsky, APL, 1991]

#### Conclusions

- Switched Biasing reduces *intrinsic* 1/f Noise

- Significant Effect (6-8dB)

- Useful in circuits and device characterisation

# Future Work (STW TEL.4756, 2 PhD cand.)

- Device Characterisation and Modelling

- Exploit effect in circuit design